Comments (11)

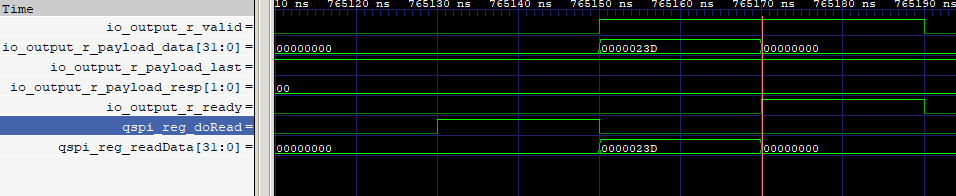

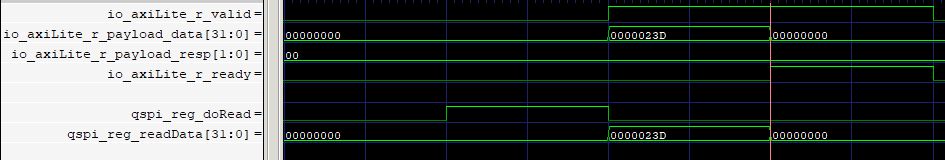

This is a R channel of axilite4 generated by regif.....

Looks good. The read data is value 0.

Or is there a reason to think that value is not expected? We cannot tell from the screenshot.

from spinalhdl.

Looks good. The read data is value 0.

Or is there a reason to think that value is not expected? We cannot tell from the screenshot.

The Data after DoRead is 0000023D.

from spinalhdl.

from spinalhdl.

Since the data send to be changing, what type of bitfield is this? Could you provide a small example that reproduces this behaviour so that we can debug it?

from spinalhdl.

Ok, I've tested as this module:

class regAxiLite extends Component {

val io = new Bundle {

val axiLite = slave(AxiLite4(32, 32))

}

val busIf = AxiLite4BusInterface(io.axiLite, (0x000, 48 Bytes), "Test_axilite")

val test0 = busIf.newReg("Test_reg")

val test0_0 = test0.field(Bool(), RW, 1)

val test0_1 = test0.field(Bool(), RW, 0)

val test0_2 = test0.field(Bool(), RW, 1)

val test0_3 = test0.field(Bits(3 bit), RW, 7)

val test0_4 = test0.fieldAt(pos = 8, UInt(8 bit), RW, 2)

busIf.accept(RalfGenerator("header"))

}This is my test code:

object regAxiLiteSim extends App {

Config.sim.compile(new regAxiLite).doSim { dut =>

// Fork a process to generate the reset and the clock on the dut

dut.clockDomain.forkStimulus(period = 10)

SimTimeout(100000)

val port = dut.io.axiLite

port.aw.valid #= false

port.w.valid #= false

port.ar.valid #= false

port.r.ready #= false

port.b.ready #= false

sleep(1000)

dut.clockDomain.waitActiveEdge()

port.ar.valid #= true

port.ar.addr #= 0

port.ar.prot #= 0

dut.clockDomain.waitActiveEdge()

while (!port.ar.ready.toBoolean) {

dut.clockDomain.waitActiveEdge()

println("Wait for ar ready active...")

}

port.ar.valid #= false

dut.clockDomain.waitActiveEdge()

while (!port.r.valid.toBoolean) {

dut.clockDomain.waitActiveEdge()

println("Wait for r valid active...")

}

//Wait for a extra clk, it's in line with the rules, right?

println("Wait for a extra clk...")

dut.clockDomain.waitActiveEdge()

port.r.ready #= true

println("Data is " + port.r.data.toBigInt.toString())

dut.clockDomain.waitActiveEdge()

port.r.ready #= false

sleep(1000)

}

}(Sim with Verilator)

from spinalhdl.

So is there anything that I make mistake? Or anyway to solve it?

from spinalhdl.

My way to solve the problem is to go back to spinalHDL version 1.8.0b or earlier. And this works for me. Or you may wait for the issue to be fixed in later spinalHDL versions or you can develop on dev version.

from spinalhdl.

My way to solve the problem is to go back to spinalHDL version 1.8.0b or earlier. And this works for me. Or you may wait for the issue to be fixed in later spinalHDL versions or you can develop on dev version.

This problem was not introduced by 1.8.0. In fact, there is a bug. It’s just that the preservation circuit of readData did not expose this problem

old way

private def readGenerator() = {

when(askRead){

readData := ..... //readData hold

}.otherwise{

readError := False

}

}

}after 1.8.0

private def readGenerator() = {

when(askRead){

readData := .....

}.otherwise{

readData := readDefaultValue //rdata cannot be retained, otherwise there will be security risks , SO KEEP 0 or defualtValue

readError := False

}

}

}so the fundamental solution is to modify lib/bus/regif/BusIfAdapter/AxiLite4BusInterfa

from spinalhdl.

My way to solve the problem is to go back to spinalHDL version 1.8.0b or earlier. And this works for me. Or you may wait for the issue to be fixed in later spinalHDL versions or you can develop on dev version.

This problem was not introduced by 1.8.0. In fact, there is a bug. It’s just that the preservation circuit of readData did not expose this problem old way

I'm not convinced this is the correct fix.

Do you have a minimal example exposing the bug?

from spinalhdl.

I see, the new code resets readData in the wrong state of the transaction.

See my comment on 230ab60.

My suggestion is to revert that commit.

from spinalhdl.

fix by expand askread cycle for workround .

val askRead = axiAr.valid || (axiR.valid && !axiR.ready)

from spinalhdl.

Related Issues (20)

- False assertion error after elaboration failure HOT 4

- Is here any easy way to connect two bus with bits only? HOT 2

- Are there Some methods to get the specified type in SpinalHDL HOT 4

- SdramXdrDdr2SpinalSim: Error "CLOCK CROSSING VIOLATION" detected in phase PhaseCheckCrossClock HOT 4

- VCS runFlags unable to pass into the simulation HOT 2

- Bugs about the SignedDivider in Divider.scala

- facility to enhance pcie dma. HOT 15

- SpinalHDL wth Vivado Issue: Generation of vivdao script failed HOT 3

- Why does the switch generate verilog code for if else? HOT 3

- SV/Verilog code generation bug HOT 1

- when I use withXSim there happend A fatal error in java runtime HOT 1

- `slave()` seem's doesn't work in version 1.9.3 HOT 7

- Exception on Component Init HOT 2

- Set wave path for XSim.

- simulation RTL path from tmp HOT 2

- PackedBundle BUG? HOT 3

- How can I use "implict" add some my own method to class Bundle or some other exist class?? HOT 1

- Something wrong with "Reg" HOT 2

- Simulation fails when using Verilator of new version which requires C++14 standard HOT 2

- Use default ClockDomain without reset signal HOT 4

Recommend Projects

-

React

React

A declarative, efficient, and flexible JavaScript library for building user interfaces.

-

Vue.js

🖖 Vue.js is a progressive, incrementally-adoptable JavaScript framework for building UI on the web.

-

Typescript

Typescript

TypeScript is a superset of JavaScript that compiles to clean JavaScript output.

-

TensorFlow

An Open Source Machine Learning Framework for Everyone

-

Django

The Web framework for perfectionists with deadlines.

-

Laravel

A PHP framework for web artisans

-

D3

Bring data to life with SVG, Canvas and HTML. 📊📈🎉

-

Recommend Topics

-

javascript

JavaScript (JS) is a lightweight interpreted programming language with first-class functions.

-

web

Some thing interesting about web. New door for the world.

-

server

A server is a program made to process requests and deliver data to clients.

-

Machine learning

Machine learning is a way of modeling and interpreting data that allows a piece of software to respond intelligently.

-

Visualization

Some thing interesting about visualization, use data art

-

Game

Some thing interesting about game, make everyone happy.

Recommend Org

-

Facebook

We are working to build community through open source technology. NB: members must have two-factor auth.

-

Microsoft

Open source projects and samples from Microsoft.

-

Google

Google ❤️ Open Source for everyone.

-

Alibaba

Alibaba Open Source for everyone

-

D3

Data-Driven Documents codes.

-

Tencent

China tencent open source team.

from spinalhdl.